# IN FACULTY OF ENGINEERING

Reliability-Aware Management in Hybrid Memories: Evaluation through Scale-Model Simulation

Wenjie Liu

Doctoral dissertation submitted to obtain the academic degree of Doctor of Computer Science Engineering

Supervisor Prof. Lieven Eeckhout, PhD

Department of Electronics and Information Systems Faculty of Engineering and Architecture, Ghent University

May 2022

# IN FACULTY OF ENGINEERING

## Reliability-Aware Management in Hybrid Memories: Evaluation through Scale-Model Simulation

Wenjie Liu

Doctoral dissertation submitted to obtain the academic degree of Doctor of Computer Science Engineering

Supervisor Prof. Lieven Eeckhout, PhD

Department of Electronics and Information Systems Faculty of Engineering and Architecture, Ghent University

May 2022

ISBN 978-94-6355-595-1 NUR 980, 987 Wettelijk depot: D/2022/10.500/36

### Members of the Examination Board

#### Chair

Prof. Filip De Turck, PhD, Ghent University

#### Other members entitled to vote

Prof. Trevor E. Carlson, PhD, National University of Singapore, Singapore Prof. Koen De Bosschere, PhD, Ghent University Prof. Jan Fostier, PhD, Ghent University Wim Heirman, PhD, Intel ExaScience Lab Jennifer Sartor, PhD, Ghent University

### Supervisor

Prof. Lieven Eeckhout, PhD, Ghent University

To my family

## Contents

| A        | cknov | wledge  | ments                                           | vii   |

|----------|-------|---------|-------------------------------------------------|-------|

| Sı       | ımma  | ary     |                                                 | ix    |

| Sa       | men   | vatting | r<br>5                                          | xiii  |

| Li       | st of | Figure  | es                                              | xvii  |

| Li       | st of | Tables  | 5                                               | xxi   |

| Li       | st of | Abbre   | eviations                                       | xxiii |

| 1        | Intr  | oducti  | on                                              | 1     |

|          | 1.1   | Motiva  | ation                                           | . 1   |

|          |       | 1.1.1   | Soft Error Reliability in Hybrid Memory Systems | . 1   |

|          |       | 1.1.2   | Large-Scale System Simulation                   | 2     |

|          |       | 1.1.3   | Managed Language Simulation                     | . 3   |

|          | 1.2   | Key C   | ontributions                                    | 4     |

|          | 1.3   | Struct  | ure and Overview                                | 8     |

| <b>2</b> | Bac   | kgrour  | nd                                              | 11    |

|          | 2.1   | Memo    | ry System Trends                                | 11    |

|          |       | 2.1.1   | DRAM Challenges                                 | 11    |

|          |       | 2.1.2   | Emerging Memory Technologies                    | 12    |

|          |       | 2.1.3   | Hybrid HBM-DRAM Memory System                   | 15    |

|          | 2.2   | System  | n Reliability                                   | 15    |

|   |     | 2.2.1   | Terminology $\ldots \ldots 1$ | 6 |

|---|-----|---------|-----------------------------------------------------------------------------------------------------|---|

|   |     | 2.2.2   | Fault-Tolerant Techniques for Memory                                                                | 7 |

|   |     | 2.2.3   | Metrics                                                                                             | 8 |

|   |     | 2.2.4   | Architecture Vulnerability Factor Analysis                                                          | 9 |

|   | 2.3 | System  | a Simulation $\ldots \ldots 2$       | 3 |

|   |     | 2.3.1   | Functional versus Timing Simulation                                                                 | 3 |

|   |     | 2.3.2   | Trace-Driven versus Execution-Driven Simulation 2                                                   | 5 |

|   |     | 2.3.3   | Workload versus Architecture Scaling Simulation 2                                                   | 6 |

|   | 2.4 | Perfor  | mance Modeling                                                                                      | 8 |

|   |     | 2.4.1   | Machine Learning based Modeling 2                                                                   | 8 |

|   |     | 2.4.2   | Analytical Modeling 2                                                                               | 8 |

|   | 2.5 | Java V  | Vorkload Benchmarking                                                                               | 9 |

| 3 | Dal | ability | -Aware Garbage Collection for Hybrid HBM-DRAM                                                       |   |

| J |     | nories  | -Aware Garbage Conection for Hybrid HDM-DITAM                                                       | 1 |

|   | 3.1 | Introd  | uction                                                                                              | 2 |

|   | 3.2 | Exploi  | ting High-Bandwidth Memory                                                                          | 5 |

|   |     | 3.2.1   | 3D-Stacked Memory                                                                                   | 5 |

|   |     | 3.2.2   | Managing HBM in Hardware 3                                                                          | 5 |

|   |     | 3.2.3   | Managing HBM in the OS                                                                              | 6 |

|   | 3.3 | Backg   | round                                                                                               | 7 |

|   |     | 3.3.1   | Soft Error Reliability                                                                              | 7 |

|   |     | 3.3.2   | Managed Runtimes                                                                                    | 8 |

|   | 3.4 | Hotnes  | ss and Risk Prediction                                                                              | 9 |

|   |     | 3.4.1   | Distribution of Hotness and Risk                                                                    | 0 |

|   |     | 3.4.2   | Allocation-Site Homogeneity 4                                                                       | 0 |

|   | 3.5 | Reliab  | ility-Aware Garbage Collection                                                                      | 2 |

|   |     | 3.5.1   | Overview                                                                                            | 2 |

|   |     | 3.5.2   | Profiling                                                                                           | 2 |

|   |     | 3.5.3   | Allocation Site Classification                                                                      | 4 |

|   |     | 3.5.4   | Bytecode Generation                                                                                 | 5 |

|   |     | 3.5.5   | Heap Organization                                                                                   | 6 |

|   | 3.6 | Experi  | imental Setup                                                                                       | 8 |

|   |     |         |                                                                                                     |   |

|   | 3.7  | Result  | S                                                                    | 51 |

|---|------|---------|----------------------------------------------------------------------|----|

|   |      | 3.7.1   | Key Trade-Offs                                                       | 51 |

|   |      | 3.7.2   | Soft Error Rate                                                      | 53 |

|   |      | 3.7.3   | Performance                                                          | 54 |

|   |      | 3.7.4   | RR-M versus Performance-Focused GC $\ . \ . \ . \ .$                 | 57 |

|   |      | 3.7.5   | Memory and Demographic Analysis                                      | 57 |

|   | 3.8  | Evalua  | ation on Real Hardware                                               | 58 |

|   | 3.9  | Other   | Related Work                                                         | 59 |

|   | 3.10 | Conclu  | usion                                                                | 59 |

| 4 | Scal | e-Mod   | lel Architectural Simulation                                         | 61 |

|   | 4.1  | Introd  | uction                                                               | 62 |

|   | 4.2  | Scale 1 | Model Construction                                                   | 65 |

|   | 4.3  | Scale 1 | Model Extrapolation                                                  | 66 |

|   |      | 4.3.1   | No Extrapolation                                                     | 67 |

|   |      | 4.3.2   | Machine Learning-based Prediction and Regression                     | 67 |

|   | 4.4  | Exper   | imental Setup                                                        | 72 |

|   |      | 4.4.1   | Simulation Setup                                                     | 72 |

|   |      | 4.4.2   | Workloads                                                            | 72 |

|   | 4.5  | Evalua  | ation                                                                | 73 |

|   |      | 4.5.1   | Scale Model Construction                                             | 73 |

|   |      | 4.5.2   | Scale Model Extrapolation                                            | 74 |

|   |      | 4.5.3   | Heterogeneous Workload Mixes                                         | 74 |

|   |      | 4.5.4   | Simulation Speedup                                                   | 77 |

|   | 4.6  | Sensit  | ivity Analyses                                                       | 79 |

|   |      | 4.6.1   | Memory bandwidth scaling $\ldots \ldots \ldots \ldots \ldots \ldots$ | 79 |

|   |      | 4.6.2   | Regression                                                           | 81 |

|   |      | 4.6.3   | ML model inputs                                                      | 81 |

|   |      | 4.6.4   | Multi-core scale-models under regression                             | 81 |

|   |      | 4.6.5   | Memory bandwidth utilization                                         | 83 |

|   |      | 4.6.6   | Multi-threaded workloads                                             | 83 |

|   | 4.7  | Relate  | ed Work                                                              | 83 |

|   | 4.8  | Conclu  | usion                                                                | 86 |

| 5  | Arc<br>tem |         | ral Simulation of Reliability-Aware | Memory | $\mathbf{Sys}$ | -<br>87 |

|----|------------|---------|-------------------------------------|--------|----------------|---------|

|    | 5.1        | Introd  | uction                              |        |                | 88      |

|    | 5.2        | Motiva  | ation and Opportunity               |        |                | 90      |

|    |            | 5.2.1   | Multicore Simulation                |        |                | 90      |

|    |            | 5.2.2   | Java Workload Simulation            |        |                | 91      |

|    |            | 5.2.3   | CPI Stacks                          |        |                | 92      |

|    | 5.3        | Experi  | mental Setup                        |        |                | 92      |

|    |            | 5.3.1   | Simulator and Java Virtual Machine  |        |                | 92      |

|    |            | 5.3.2   | Simulated Processor Architectures   |        |                | 92      |

|    |            | 5.3.3   | Workloads                           |        |                | 93      |

|    |            | 5.3.4   | Scale-Model Simulation              |        |                | 94      |

|    | 5.4        | Evalua  | ution                               |        |                | 94      |

|    |            | 5.4.1   | CPI Stacks                          |        |                | 95      |

|    |            | 5.4.2   | Model Selection                     |        |                | 97      |

|    |            | 5.4.3   | Performance                         |        |                | 98      |

|    |            | 5.4.4   | Large Target System Prediction      |        |                | 100     |

|    | 5.5        | Conclu  | usion                               |        |                | 101     |

| 6  | Con        | clusior | n and Future Work                   |        |                | 103     |

|    | 6.1        | Summ    | ary                                 |        |                | 103     |

|    | 6.2        | Future  | Work                                |        |                | 105     |

| Bi | bliog      | graphy  |                                     |        |                | 109     |

### Acknowledgements

Doing a Ph.D. has been a dream since I am a master student. Reading my Ph.D. abroad, however, was not the original plan and finally became an extra gift of my life. Thanks to Professor Zhiying Wang, I began to think about the possibility of studying abroad and took my first step to work on it. Thanks to Professor Lieven Eeckhout, I got the opportunity to do research and finish my Ph.D. at Ghent University. I have delayed writing this part until the last minute because there are so many lovely people along my Ph.D. journey and I cannot thank them enough in a few words.

I want to express my deep gratitude to my advisor, Professor Lieven Eeckhout, for his valuable guidance and strong support during my Ph.D. I still remember the introductions of Lieven by my colleagues about how kind a person he is and how professional he is as a researcher. Working with him in the last four years proves that he totally deserves these compliments and he is much better. He is a hardworking and responsible advisor. He guides me how to conduct impactful research in a systematic manner. Although he is very busy, he continues to provide extensive feedback on my research, on the paper writings, and even on the presentations. Both his guidance and his work attitude inspired me and helped me become a better researcher. He is also a very caring person. I will never forget his unconditional support when I was stuck with some family issues and work pressure during the Covid outbreak. He gave me enough room to deal with my private life and provided many practical solutions to my dilemma. Without his patience, encouragement and support, I cannot imagine how to go through those tough times and finally finish my Ph.D. successfully.

Many thanks to Shoaib Akram, who played an important role in the early days of my Ph.D. life. I have been working with Shoaib in the first two years of my Ph.D., and he really gave me many suggestions on the research. He taught me to conduct valuable and interesting research instead of only focusing on paper publications. He encouraged me to insist on solving a challenging problem instead of giving up too early. His perfectionism at every step of research impressed me and inspired me to develop good research habits like him.

I want to thank all the members in my examination committee who read my thesis carefully and delivered valuable feedback despite their busy schedules. Very special thanks to Jennifer B. Sartor and Wim Heirman. I have been working with Jennifer for my first project. She listened to my work progress patiently and gave me practical suggestions whenever I needed. I met Wim when I was stuck with some simulator issues. Wim is very professional in the field of performance modeling and I benefited a lot from his sharpness in the computer architecture design.

Many thanks to my colleagues in PerfLab: Ajeva Naithani, Yuxi Liu, Josue Feliu, Xia Zhao, Lu Wang, Shiqing Zhang, Jaime Roelandts, Almutaz Adileh, Seyyed Hossein SeyyedAghaei Rezaei, Cecilia Gonzalez-Alvarez, Sander De Pestel, Sam Van den Steen, Shoaib Akram, Kartik Lakshminarasimhan, Mahmood Naderan-Tahan, Saeideh Sheikhpour and Benyamin Eslami. I am lucky to work with them in the past four years as we spent so many happy hours in the office. I want to thank Ajeya for his help with cluster-related issues and his generous sharing of the experience on Ph.D. defense. I am very grateful to have Yuxi, Xia, Lu, and Shiqing around in Ghent. Yuxi and Xia gave me sincere suggestions on my research topics. Lu offered me considerable help to settle in Ghent. Her kindness lightened the early days of my Ph.D. life. Shiqing is always there for me, getting up early to help me test the meeting device and congratulating me on passing the internal defense. I would also like to thank the department staff for their help with administrative and technical issues. Special thanks to Marnix for the help with arranging conference travels and many thanks to Vicky and Inge for their help with various work/life related paperwork.

I thank all my friends in Ghent: Xiaodong Liu, Yun Zhou, Yuhui Wu, Sheng Yang, Xiangyu Xue, Qiming Sun, Lei Luo, Xin Cheng, Boxuan Gao, Yan Li, etc. The happy moments spending with them made my life abroad precious and unforgettable. I really cherish our friendship. I am so lucky to have Xiaodong as my roommate in the last four years. We shared ups and downs studying abroad and we supported each other whenever needed. I will never forget our heart-to-heart talks. Yun and I prepared for the Ph.D. defense at the same time, and we worked late together for the submission deadline. Her accompany relieves me a lot from the anxiety of defense preparation. I also want to thank my previous Chinese advisor in NUDT, Prof. Zhiying Wang. He encouraged me to read Ph.D. abroad and helped me apply the CSC scholarship.

Finally, I want to thank my parents for raising me and giving me endless love. Their love, wisdom, care, and strength have meant to the world to me. May good luck follow my little brother for his forthcoming GaoKao. I also want to thank my husband, Jianglong Song. If I could choose anybody at all to back me up through all the difficulties of life, it would be my husband a hundred times over. It's been ten years since we were together and thank you for always being the most reliable and supportive people to me.

> Wenjie Liu Gent, May 16, 2022

### Summary

Emerging computer applications require increasing memory capacity as well as increasing bandwidth to the memory system. Unfortunately, traditional DRAM memories are constrained by the limited scalability of new chip technologies due to the decreasing reliability of individual memory cells and increasing manufacturing complexity. Consequently, computer architects must consider alternative memory technologies in order to meet the large capacity and high bandwidth requirements. Recently introduced 3D-stacked memories, such as *High-Bandwidth Memory (HBM)* in which different memory chips are placed one above the other, provide considerably higher bandwidth and lower access time at a relatively low cost. However, 3D-stacked memories have the disadvantages that capacity is limited and that reliability is inferior to conventional DRAM memories due to the higher density of memory cells. Temporary errors (e.g., soft errors or transient faults) due to cosmic rays or energy particles can lead to incorrect executions. In order to circumvent the limitations of different memory technologies, researchers have proposed hybrid memories in which, for example, a 3D-stacked memory is combined with a conventional DRAM memory. This makes it possible to offer high bandwidth (thanks to the 3D-stacked memory) and high capacity (thanks to the DRAM memory). However, the reliability of hybrid memory is limited by the weakest link, namely the 3D-stacked memory.

A concrete practical problem that arises when evaluating and exploring new architectural ideas, for example, the evaluation of hybrid memory systems, is that current simulation methodologies are inadequate. The most commonly used methodology is to model every detail of the design in a cycle-accurate manner, leading to a number of experimental problems. More specifically, the simulation time explodes when large systems have to be modeled, for example when dozens of processor cores have to be simulated for modeling a future *multicore* processor. In some cases, it is even impossible to simulate such large systems due to limitations in computing or memory capacity on the server on which the simulation problem, such as sampling of the execution and modeling at a higher abstraction level, do not fundamentally solve the problem and are therefore inadequate. This doctoral thesis makes two contributions regarding the management and improvement of the reliability of hybrid memories, and two contributions regarding the simulation of large systems.

Homogeneity of Memory Allocation. Several modern programming languages use automatic memory management (e.g., *garbage collection*) to improve the productivity of the software developer and the reliability of the resulting software. Garbage collection manages memory at the level of individual objects. In this PhD thesis, we classify objects according to two criteria, namely *hotness* and *risk*, in order to map their impact on performance and reliability, respectively. Allocating hot objects in the 3D-stacked memory of a hybrid memory system offers a performance advantage (due to higher bandwidth), while allocating risky objects in the 3D-stacked memory leads to an increased vulnerability (due to less reliability). We propose to allocate objects in the 3Dstacked memory versus the conventional DRAM memory in a hybrid memory system based on the hotness and risk of those objects. Our analysis shows that the hotness and risk of an object are only weakly correlated. Consequently, it is crucial to consider both the hotness and risk. The first important contribution of this doctoral thesis consists of demonstrating that the location in the code where an object is allocated (i.e., allocation site) is a very accurate predictor of the hotness and risk of the object. In other words, all objects that are allocated from the same location in the program code show a similar hotness/risk profile. We refer to this property as the homogeneity of the memory allocation. We exploit this important finding in the second contribution.

Reliability-Aware Memory Management. Hybrid memory systems allow us to combine the advantages of both memory technologies and suppress the drawbacks. The advantage of the 3D-stacked memory in a hybrid memory system is the high bandwidth offered, while the disadvantages concern limited capacity and reliability. The drawbacks can be overcome by reliabilityaware memory management (i.e., reliability-aware garbage collection). The basic idea behind reliability-aware memory management is to allocate objects in 3D-stacked memory only if those objects are hot (i.e., they are frequently accessed) and lead to a rather limited risk in terms of reliability. We propose two variants of reliability-aware memory management, namely RiskRelief-Nursery (RR-N) and RiskRelief-Mature (RR-M). RR-N places all newly allocated objects (allocated in the so-called nursery space) in the 3D-stacked memory; older objects in the mature space that were allocated some time ago and are still reachable are placed in the DRAM memory. RR-M also makes a distinction for the mature space where hot and relatively risk-free objects are also placed in the 3D-stacked memory. Whether or not an object is hot and risky (and therefore should be placed in the 3D-stacked memory), is determined by the place where this object was allocated in the program code (first contribution of the thesis). Reliability-aware memory management in a hybrid memory system significantly improves reliability compared to a memory system that only consists of 3D-stacked memory, and at the same time improves the performance compared to a memory system only consisting of conventional DRAM memory.

More specifically, RR-N and RR-M improve the reliability by a factor of  $18 \times$  and  $9 \times$  compared to a 3D-stacked memory, and improve performance by 20% and 29% over a conventional memory system, respectively.

Scale-Model Simulation. To address the fundamental simulation problem of future large systems (which we also encountered in the evaluation of the second contribution), we propose a new methodology for predicting the performance of large systems based on small scale models. A scale model is in fact a miniaturized version of the large system that, because of its limited scale, can easily be simulated with existing simulation techniques. The performance obtained from the simulated scale model is then extrapolated to make a prediction for the larger system. The question arises how to construct a scale model and then extrapolate it. We show that different shared resources, such as the shared caches, the interconnection network and the shared memory bandwidth, should be scaled proportionally in the scale model. To extrapolate the performance of the scale model, we use machine learning (ML) techniques and we consider two variants, namely ML-based prediction and ML-based regression. ML-based prediction requires a number of simulations of the target system as input for training the ML model, while ML-based regression only requires simulations of a number of scale models (and thus not of the much larger target system). ML-based regression is therefore suitable in situations where it is impossible to simulate the target system. Predicting a multicore system with 32 processor cores based on a scale model with a single processor core results in a reduction of the simulation time by a factor of  $28 \times$ . ML-based prediction and regression lead to a relative prediction error of 6.4% and 8.0%, respectively.

Scale Models for Reliability-Aware Memory Management. In the fourth and final contribution, we apply the simulation and prediction methodology based on scale models to the evaluation of reliability-aware memory management. As mentioned earlier, it was not possible to rigorously evaluate our second contribution with existing simulation methodologies because the target system is too large to simulate (32 processor cores with a hybrid memory system). Consequently, in the initial evaluation of the second contribution, we had to resort to the simulation of a proportional scale model without MLbased prediction or regression. When we fully apply the newly proposed scale model simulation methodology (the third contribution) to the evaluation of reliability-aware memory management, we conclude that the obtained performance predictions based on a proportional scale model were conservative. More specifically, we show that the performance improvement reported above for a hybrid memory system with RiskRelief memory management over a conventional memory system is an underestimation of the expected performance improvement. Based on our prediction, we expect that a hybrid memory system with RR-N and RR-M memory management improves performance by 62%(instead of 20%) and 68% (instead of 29%) over conventional memory, respectively.

### Samenvatting

Hedendaagse computertoepassingen vereisen steeds meer geheugencapaciteit alsook steeds grotere bandbreedte tot het geheugensysteem. Jammer genoeg zijn traditionele DRAM-geheugens gelimiteerd door de beperkte schaalbaarheid naar nieuwe chiptechnologieën wegens een steeds afnemende betrouwbaarheid van de individuele geheugencellen en een steeds toenemende productiecomplexiteit. Bijgevolg moeten computerarchitecten alternatieve geheugentechnologieën beschouwen teneinde aan de hoge capaciteiten bandbreedtevereisten te kunnen voldoen. Recentelijk geïntroduceerde 3Dgeheugens, zoals bijvoorbeeld High-Bandwidth Memory (HBM) waarbij verschillende geheugenchips boven elkaar geplaatst worden, leveren aanzienlijk hogere bandbreedte en lagere toegangstijd aan relatief lage kost. 3D-geheugens hebben echter als nadeel dat de capaciteit beperkt is en de betrouwbaarheid inferieur is in vergelijking met conventionele DRAM-geheugens wegens de hogere densiteit van geheugencellen. Tijdelijke fouten (Eng. soft errors of transient errors) ten gevolge van kosmische straling of energiedeeltjes kunnen leiden tot incorrecte uitvoeringen. Teneinde de beperkingen van verschillende geheugentechnologieën te omzeilen, hebben onderzoekers hybride geheugens voorgesteld waarbij bijvoorbeeld een 3D-geheugen gecombineerd wordt met een DRAMgeheugen. Dit laat toe hoge bandbreedte (dankzij het 3D-geheugen) én hoge capaciteit (dankzij het DRAM-geheugen) aan te bieden. Echter, de betrouwbaarheid van hybride geheugens is beperkt door de zwakste schakel, namelijk het 3D-geheugen.

Een concreet praktisch probleem dat zich stelt bij het evalueren en exploreren van nieuwe architecturale ideeën, zoals bijvoorbeeld de evaluatie van hybride geheugensystemen, is dat huidige simulatiemethodologieën ontoereikend zijn. De meest gebruikte methodologie bestaat erin elk detail van het ontwerp op een cyclusgetrouwe manier te modelleren, wat leidt tot een aantal experimentele problemen. Meer bepaald explodeert de simulatietijd wanneer grote systemenen gemodelleerd moeten worden, bijvoorbeeld wanneer tientallen processorkernen (Eng. *cores*) gesimuleerd moeten worden voor het modelleren van een toekomstige *multicore* processor. In sommige gevallen is het zelfs onmogelijk om dergelijke grote systemen te simuleren wegens beperkingen qua reken- of geheugencapaciteit in de server waarop de simulaties uitgevoerd worden. Bestaande technieken om het simulatieprobleem op te lossen zoals bemonstering (Eng. *sampling*) van de uitvoering en het modelleren op een hoger abstractieniveau, bieden echter geen soelaas en zijn derhalve ontoereikend.

Deze doctoraatsthesis levert twee bijdragen m.b.t. het beheren en verbeteren van de betrouwbaarheid van hybride geheugens, en twee bijdragen m.b.t. het simuleren van grote systemen.

Homogeniteit van geheugenallocatie. Verschillende moderne programmeertalen maken gebruik van automatisch geheugenbeheer (Eng. garbage collection) teneinde de productiviteit van de software-ontwikkelaar en de betrouwbaarheid van de resulterende software te verbeteren. Garbage collection beheert het geheugen op het niveau van individuele objecten. In deze doctoraatsthesis classificeren we objecten aan de hand van twee criteria, namelijk belang (Eng. hotness) en risico (Eng. risk), teneinde hun impact op respectievelijk prestatie en betrouwbaarheid in kaart te brengen. Het alloceren van belangrijke objecten in het 3D-geheugen van een hybride geheugensysteem biedt een voordeel qua prestatie (wegens hogere bandbreedte), terwijl het alloceren van risicovolle objecten in het 3D-geheugen leidt een verhoogde kwetsbaarheid (wegens minder betrouwbaar). We stellen voor objecten te alloceren in het 3D-geheugen versus het conventioneel DRAM-geheugen in een hybride geheugensysteem op basis van het belang en risico van die objecten. Onze analyse toont aan dat het belang en het risico van een object slechts zwak gecorreleerd zijn. Bijgevolg is het cruciaal om zowel het belang als het risico in rekening te brengen. De eerste belangrijke bijdrage van deze doctoraatsthesis bestaat erin aan te tonen dat de plaats in de code waar een object gealloceerd wordt (Eng. allocation site) een zeer nauwkeurige voorspeller is van het belang en het risico van het object. M.a.w. alle objecten die gealloceerd worden vanop eenzelfde locatie in de programmacode vertonen een gelijkaardig belang/risico-profiel. We refereren naar deze eigenschap als de homogeniteit van de geheugenallocatie. Deze belangrijke vaststelling buiten we uit in de tweede bijdrage.

Betrouwbaarheidsbewust geheugenbeheer. Hybride geheugensystemen vereisen dat we de voordelen van beide geheugentechnologieën verenigen en de nadelen onderdrukken. Het voordeel van het 3D-geheugen in een hybride geheugensysteem is de hoge bandbreedte die aangeboden wordt, terwijl de nadelen beperkte capaciteit en betrouwbaarheid betreffen. De nadelen kunnen overwonnen worden door betrouwbaarheidsbewust geheugenbeheer (Eng. reliability-aware garbage collection). De basisidee achter betrouwbaarheidsbewust geheugenbeheer bestaat erin objecten in het 3D-geheugen te alloceren enkel en alleen als die objecten belangrijk zijn (d.i. frequent geconsulteerd worden) én tot een eerder beperkt risico leiden qua betrouwbaarheid. We stellen twee varianten van betrouwbaarheidsbewust geheugenbeheer voor, namelijk RiskRelief-Nursery (RR-N) en RiskRelief-Mature (RR-M). RR-N plaatst alle nieuw gealloceerde objecten (die galloceerd worden in de zogenaamde nursery adresruimte) in het 3D-geheugen; oudere objecten in de mature adresruimte die een tijd geleden gealloceerd werden en nog steeds bereikbaar zijn (m.a.w. deze objecten kunnen nog steeds geconsulteerd worden), worden in het DRAMgeheugen geplaatst. RR-M maakt daarenboven nog een onderscheid voor de mature adresruimte waarbij belangrijke en relatief risicoloze objecten eveneens in het 3D-geheugen geplaatst worden. Of een object al dan niet belangrijk en risicovol is (en dus in het 3D-geheugen geplaatst moet worden), wordt bepaald door de plaats waar dit object gealloceerd werd in de programmacode (eerste bijdrage van de thesis). Betrouwbaarheidsbewust geheugenbeheer verbetert de betrouwbaarheid aanzienlijk t.o.v. een geheugensysteem dat enkel uit 3D-geheugen zou bestaan, en verbetert tegelijkertijd de prestatie t.o.v. een geheugensysteem dat enkel uit conventioneel DRAM geheugen bestaat. Meer bepaald verbeteren RR-N en RR-M de betrouwbaarheid met een factor van respectievelijk  $18 \times$  en  $9 \times$  t.o.v. een 3D-geheugen. RR-N en RR-M verbeteren de prestatie met respectievelijk 20% en 29% t.o.v. een conventioneel geheugen-systeem.

Simulatie van schaalmodellen. Teneinde het fundamentele probleem van de simulatie van toekomstige grote systemen aan te pakken (waar we eveneens op gestoten zijn bij de evaluatie van de tweede bijdrage), stellen we een nieuwe methodologie voor voor het voorspellen van de prestatie van grote systemen op basis van kleine schaalmodellen. Een schaalmodel is in feite een geminiaturiseerde versie van het grote systeem dat wegens zijn beperkte schaal eenvoudig te simuleren valt met bestaande simulatietechnieken. De prestatie bekomen op basis van het gesimuleerde schaalmodel wordt vervolgens geëxtrapoleerd teneinde een voorspelling te maken voor het groter systeem. De vraag stelt zich hoe een schaalmodel te construeren en vervolgens te extrapoleren. We tonen aan dat de verschillende gedeelde componenten (Eng. shared resources), zoals de gemeenschappelijk caches, het interconnectienetwerk en de gedeelde geheugenbandbreedte, best proportioneel geschaald worden in het schaalmodel. Voor het extrapoleren van de prestatie van het schaalmodel maken we gebruik van machine learning (ML), en we beschouwen twee varianten, namelijk ML-gebaseerde voorspelling en ML-gebaseerde regressie. MLgebaseerde voorspelling vereist een aantal simulaties van het doelsysteem als input voor het trainen van het ML-model, terwijl ML-gebaseerde regressie enkel simulaties vereist van een aantal schaalmodellen (en dus niet van het veel groter doelsysteem). ML-gebaseerde regressie is bijgevolg geschikt in situaties waarbij het onmogelijk is het doelsysteem te simuleren. Het voorspellen van een multicore systeem met 32 processorkernen op basis van een schaalmodel met een enkele processorkern levert een reductie van de simulatietijd op van een factor  $28 \times$ . ML-gebaseerde voorspelling en regressie leiden tot een relatieve voorspellingsfout van respectievelijk 6.4% en 8.0%.

Schaalmodellen voor betrouwbaarheidsbewust geheugenbeheer. In de vierde en laatste bijdrage passen we de simulatie- en voorspellingsmethodologie op basis van schaalmodellen toe op het evalueren van betrouwbaarheidsbewust geheugenbeheer. Zoals eerder aangehaald was het niet mogelijk om onze tweede bijdrage rigoureus te evalueren met bestaande simulatiemethodologieën wegens de te grote schaal van het doelsysteem (32 processorkernen met hybride geheugensysteem). Bijgevolg hebben we bij de initiële evaluatie van de tweede bijdrage onze toevlucht moeten nemen tot de simulatie van een proportioneel schaalmodel zonder ML-gebaseerde voorspelling of regressie. Wanneer we de nieuw voorgestelde simulatie- en voorspellingsmethodologie op basis van schaalmodellen (derde bijdrage) ten volle toepassen voor de evaluatie van betrouwbaarheidsbewust geheugenbeheer, concluderen we dat de bekomen prestatievoorspellingen op basis van een proportioneel schaalmodel conservatief waren. Meer specifiek tonen we aan dat de hierboven gerapporteerde prestatieverbetering voor een hybride geheugensysteem met RiskReliefgeheugenbeheer t.o.v. een conventioneel geheugensysteem een onderschatting is van de te verwachten prestatieverbetering. Op basis van onze voorspelling verwachten we dat een hybride geheugensysteem met RR-N en RR-M geheugenbeheer de prestatie verbeteren met respectievelijk 62% (i.p.v. 20%) en 68% (i.p.v. 29%) ten opzichte van een conventioneel geheugen.

# List of Figures

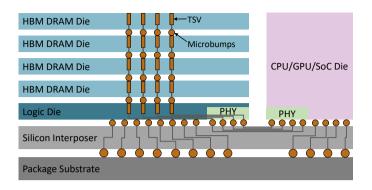

| 2.1 | HBM architecture: HBM vertically stacks multiple DRAM dies<br>which are interconnected by microscopic wires called through-<br>silicon vias (TSVs)                                                                                                                                                                                                                                 | 14 |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2 | Assumed memory and the computer system level hierarchy                                                                                                                                                                                                                                                                                                                             | 14 |

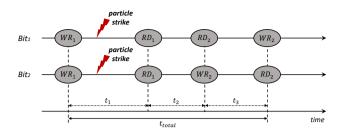

| 2.3 | AVF of two bits in the memory system. Two bits in the memory<br>could have the same hotness but different AVFs depending on the<br>sequence of reads and writes.                                                                                                                                                                                                                   | 22 |

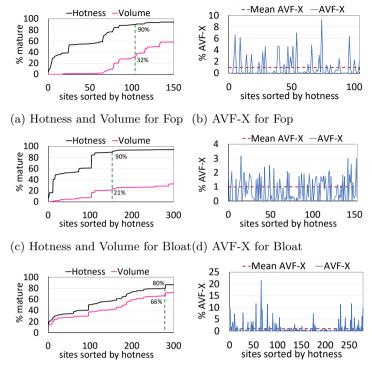

| 3.1 | Distribution of hotness and mature heap volume by allocation<br>site (left column), versus risk for the top hottest allocation sites<br>(right column) for Fop (top), Bloat (middle), and Pmd (bottom).                                                                                                                                                                            | 39 |

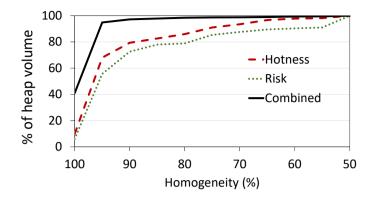

| 3.2 | Percentage heap volume as a function of allocation-site homo-<br>geneity for hotness, risk, and combined hotness and risk assum-<br>ing a 10% cutoff threshold.                                                                                                                                                                                                                    | 41 |

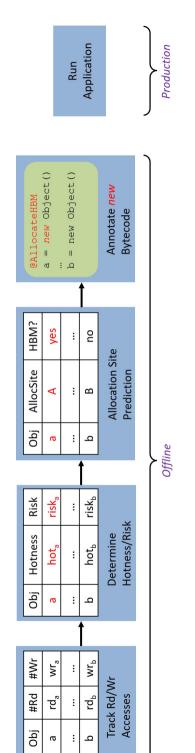

| 3.3 | Overview of RiskRelief. Offline analysis records the number of<br>reads and writes to all objects. Then, per-object hotness and<br>risk metrics are used to generate an allocation site classification<br>advice which serves as input to a bytecode rewriter. The rewriter<br>annotates hot and low-risk sites as HBM, steering the garbage<br>collector to place objects in HBM. | 43 |

| 3.4 | Example of an access trace with allocation sites in the last col-<br>umn (a), per object hotness and AVF-X (b), and prediction of<br>allocation sites using the FMID and MRAT heuristics (c).                                                                                                                                                                                      | 44 |

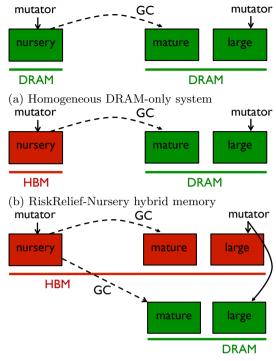

| 3.5 | Main memory heap organizations.                                                                                                                                                                                                                                                                                                                                                    | 47 |

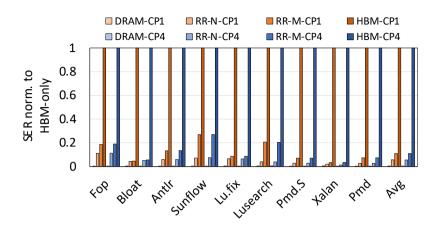

| 3.7 | Soft error rates normalized to HBM-Only for the RiskRelief col-<br>lectors and DRAM-Only through single-core and 4-core simula-<br>tions                                                                                                                                                                                                                                           | 50 |

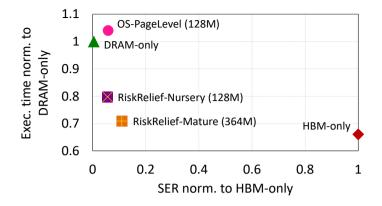

| 3.8  | The execution time versus SER trade-off for the RiskRelief col-<br>lectors and the state-of-the-art OS approach, normalized to the<br>DRAM-Only and HBM-Only systems. RiskRelief-Nursery and<br>OS approach consume 128 MB HBM. RiskRelief-Mature uses a<br>larger fraction of HBM (364 MB) by placing part of the mature<br>space in HBM as well.                                                               | 51 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

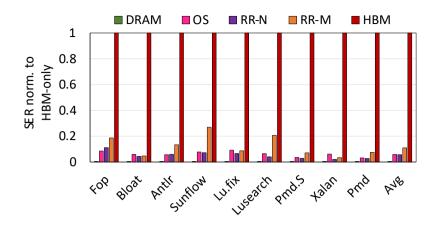

| 3.9  | Soft error rates normalized to HBM-Only for the RiskRelief col-<br>lectors, the OS approach and DRAM-Only                                                                                                                                                                                                                                                                                                        | 52 |

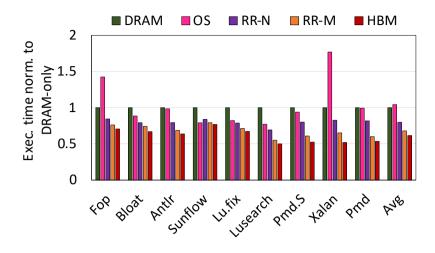

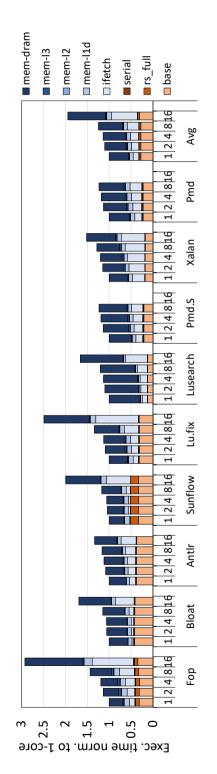

| 3.10 | Execution times normalized to DRAM-Only for the RiskRelief collectors, the OS approach and HBM-Only                                                                                                                                                                                                                                                                                                              | 53 |

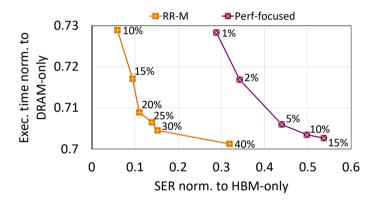

| 3.11 | Execution time versus SER trade-off for different configurations of RR-M and its performance-focused variant.                                                                                                                                                                                                                                                                                                    | 55 |

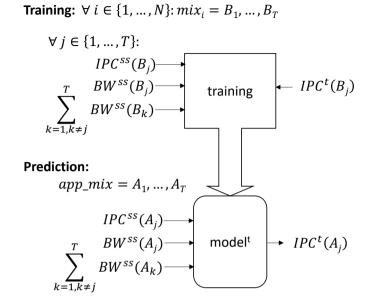

| 4.1  | ML-based prediction involves a training and prediction phase.<br>The training phase requires simulation results for the target system.                                                                                                                                                                                                                                                                           | 68 |

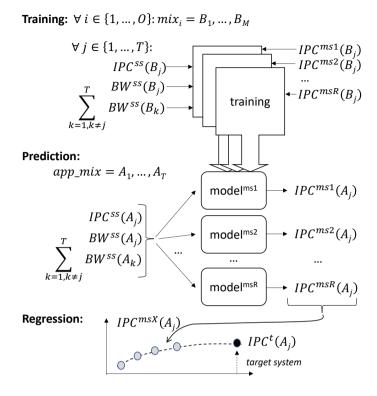

| 4.2  | ML-based regression involves a training, prediction and regression phase. The training phase requires simulation results obtained for a number of multi-core scale models, but not the target system.                                                                                                                                                                                                            | 70 |

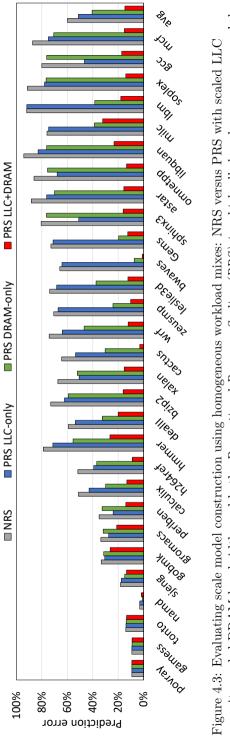

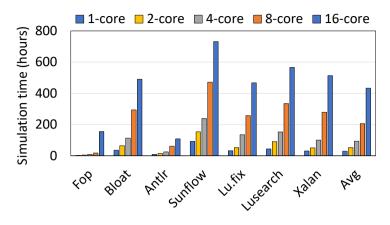

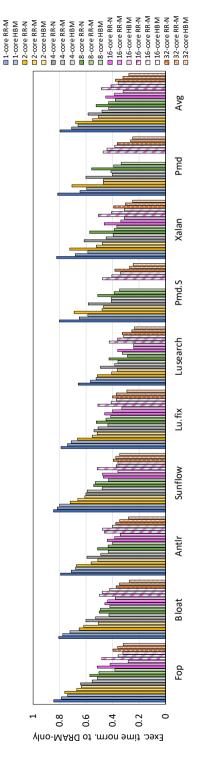

| 4.3  | Evaluating scale model construction using homogeneous work-<br>load mixes: NRS versus PRS with scaled LLC capacity, scaled<br>DRAM bandwidth, and both. <i>Proportional Resource Scaling</i><br>( <i>PRS</i> ) in which all shared resources are scaled proportionally<br>leads to the most accurate scale models                                                                                                | 75 |

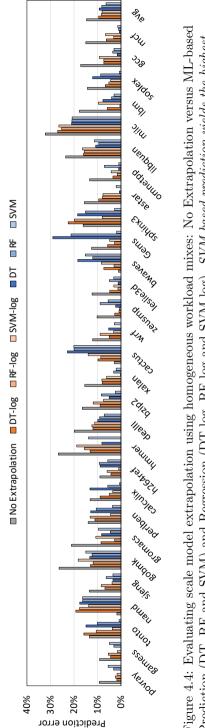

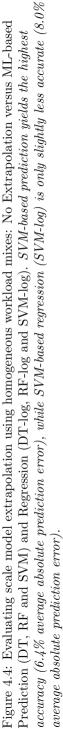

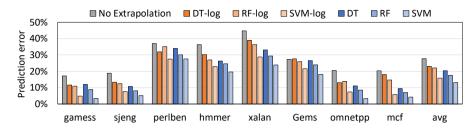

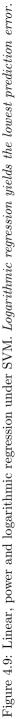

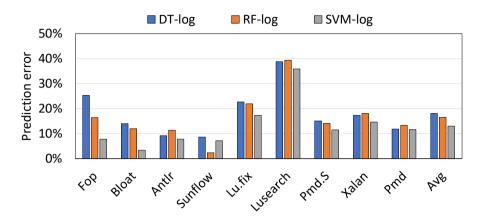

| 4.4  | Evaluating scale model extrapolation using homogeneous work-<br>load mixes: No Extrapolation versus ML-based Prediction (DT,<br>RF and SVM) and Regression (DT-log, RF-log and SVM-log).<br>SVM-based prediction yields the highest accuracy (6.4% average<br>absolute prediction error), while SVM-based regression (SVM-<br>log) is only slightly less accurate (8.0% average absolute predic-<br>tion error). | 76 |

| 4.5  | Evaluating scale model extrapolation using heterogeneous work-<br>load mixes: No Extrapolation versus ML-based Prediction (DT,<br>RF and SVM) and Regression (DT-log, RF-log and SVM-log).<br>The SVM-based Prediction method yields the highest accuracy<br>(13.2% average prediction error), while SVM-based Regression<br>(SVM-log) is only slightly less accurate (15.8% average predic-<br>tion error).     | 77 |

| 4.6  | STP prediction error for ML-based regression across a total<br>of 80 heterogeneous workload mixes. <i>SVM-log predicts system</i><br><i>throughput (STP) with an average prediction error of 3.8% and</i>                                                                                                                                                                                                        |    |

|      | at most 13.0%.                                                                                                                                                                                                                                                                                                                                                                                                   | 78 |

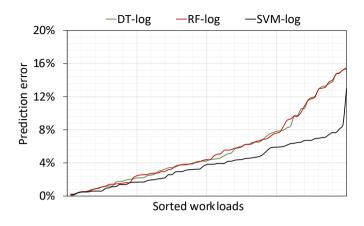

| 4.7  | Prediction error versus simulation speedup. SVM-based predic-<br>tion and regression achieve high prediction accuracy while yield-<br>ing high simulation speedups.                                                                                                                                                                                                                           | 78 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

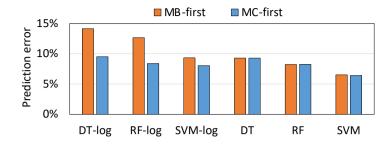

| 4.8  | Evaluating memory bandwidth scaling alternatives under PRS. <i>ML-based regression achieves higher accuracy by first scaling the number of memory controllers ('MC-first') compared to first scaling memory bandwidth per memory controller ('MB-first')</i>                                                                                                                                  | 79 |

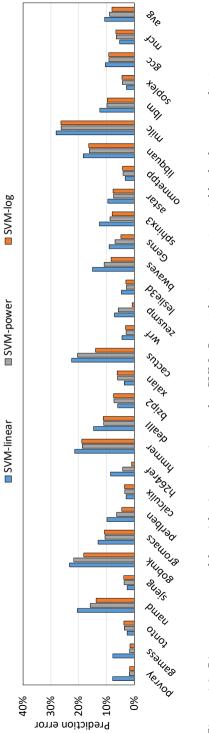

| 4.9  | Linear, power and logarithmic regression under SVM. Logarith-<br>mic regression yields the lowest prediction error.                                                                                                                                                                                                                                                                           | 80 |

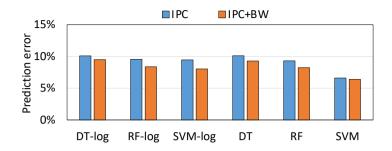

| 4.10 | Varying the input variables to the ML-based extrapolation tech-<br>niques. Considering both performance and bandwidth utilization<br>as input variables leads to improved accuracy compared to using<br>only performance as input.                                                                                                                                                            | 81 |

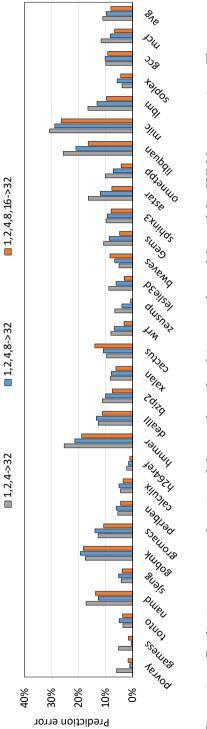

| 4.11 | Prediction error as a function of the number of multi-core scale models used for SVM-log regression. <i>The prediction error only slightly increases with a reduced number of multi-core scale models.</i>                                                                                                                                                                                    | 82 |

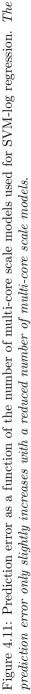

| 4.12 | Prediction error for predicting memory bandwidth utilization.<br>SVM and SVM-log predict memory bandwidth utilization with<br>an average error of 8.7% and 11.3%, respectively                                                                                                                                                                                                                | 84 |

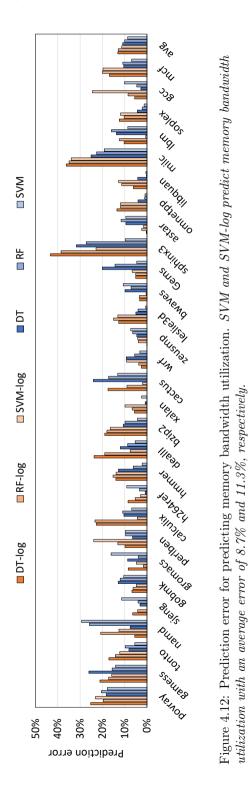

| 5.1  | Simulation time in hours for multiprogram Java workloads with<br>up to 16 cores on Sniper. Simulation time of multiprogram work-<br>loads is prohibitive and increases super-linearly with an increas-<br>ing number of cores.                                                                                                                                                                | 89 |

| 5.2  | The CPI stacks for multi-core systems normalized to a single-<br>core system. The instruction fetch latency and DRAM access<br>latency have a large contribution to CPI and keep increasing with<br>system scaling. The access latency to last-level cache (LLC) also<br>has a significant increase with increased core counts but it only<br>takes 1% of the total execution time on average | 96 |

| 5.3  | Prediction error for the 8-core system using ML-based regression<br>models. SVM with logarithmic regression (SVM-log) yields the<br>highest prediction accuracy with an average prediction error of<br>13.0% and at most 35.8%                                                                                                                                                                | 97 |

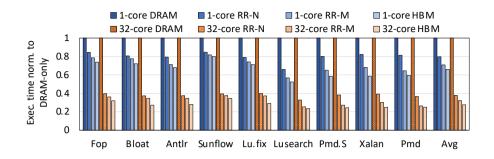

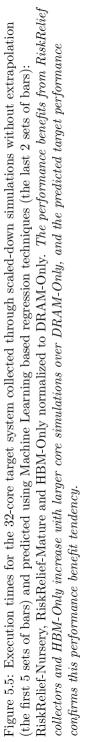

| 5.4  | Scaled and predicted 32-core execution time normalized to DRAM-Only for the RiskRelief collectors and HBM-Only. The 1-core performance results are obtained from a single-core system with all shared resources scaled down proportionally. The 32-core performance results are predicted using small-core simulation results and the SVM-log regression model                                | 98 |

# List of Tables

| 2.1 | Relationship between minimum Hamming distance and number<br>of bit errors that can be detected and corrected.                                                                                                                                                                            | 17 |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.1 | Simulated system parameters                                                                                                                                                                                                                                                              | 49 |

| 3.2 | The number of page migrations (DRAM to HBM, HBM to DRAM, and total), the number of 100 ms migration epochs, and the number of page migrations per epoch for the OS approach.                                                                                                             | 55 |

| 3.3 | Object demographics: total allocation, heap size, nursery survival rates, and average and maximum mature heap usage (in MB) for our 32-instance workloads                                                                                                                                | 56 |

| 4.1 | Constructing scale models through <i>Proportional Resource Scaling</i> : LLC capacity in MB; on-chip interconnection network in GB/s: number of cross-section links (CSLs) and bandwidth per CSL; main memory bandwidth in GB/s: number of memory controllers (MCs) and bandwidth per MC | 65 |

| 4.2 | Target system.                                                                                                                                                                                                                                                                           | 71 |

| 5.1 | Target system parameters                                                                                                                                                                                                                                                                 | 93 |

# List of Abbreviations

| ACE                                    | Architecturally Correct Execution  |  |

|----------------------------------------|------------------------------------|--|

| AI                                     | Artificial Intelligence            |  |

| AVF                                    | Architectural Vulnerability Factor |  |

| CPI                                    | Cycles Per Instruction             |  |

| CPU                                    | Central Processing Unit            |  |

| $\mathbf{CSL}$                         | Cross-Section Link                 |  |

| DRAM                                   | Dynamic Random Access Memory       |  |

| DT                                     | Decision Tree                      |  |

| <b>ECC</b> Error Correction Code       |                                    |  |

| FeRAM Ferroelectric Random-Access Memo |                                    |  |

| <b>FIT</b> Failure In Time             |                                    |  |

| FMID                                   | Fixed-Midpoint                     |  |

| GB                                     | Giga Byte                          |  |

| $\mathbf{GC}$                          | Garbage Collection                 |  |

| GP                                     | General Purpose                    |  |

| HBM                                    | High-Bandwidth Memory              |  |

| HMC Hybrid Memory Cube                 |                                    |  |

| <b>IPC</b> Instructions Per Cycle      |                                    |  |

| ISA                                    | Instruction-Set Architecture       |  |

| JIT                                    | Just-In-Time                       |  |

| JVM                                    | Java Virtual Machine               |  |

| KB                                       | B Kilo Byte                            |  |

|------------------------------------------|----------------------------------------|--|

| L1I                                      | Level-1 Instruction Cache              |  |

| L1D                                      | Level-1 Data Cache                     |  |

| L2                                       | Level-2 Cache                          |  |

| L3                                       | Level-3 Cache                          |  |

| LLC                                      | Last-Level Cache                       |  |

| LOS                                      | Large Object Space                     |  |

| MB                                       | Mega Byte                              |  |

| $\mathbf{MC}$                            | Memory Controller                      |  |

| $\mathbf{ML}$                            | Machine Learning                       |  |

| MPKI                                     | Misses Per Kilo Instructions           |  |

| MRAM                                     | Magneto-Resistive Random-Access Memory |  |

| MRAT                                     | Moving-Ratio                           |  |

| MTTF                                     | Mean Time To Failure                   |  |

| MTBF                                     | Mean Time Between Failures             |  |

| NAND                                     | ND NOT-AND                             |  |

| NoC                                      | Network-on-Chip                        |  |

| NRS                                      | No Resource Scaling                    |  |

| NUCA                                     | Non-Uniform Cache Architectures        |  |

| NUMA                                     | Non-Uniform Memory Access              |  |

| NVM                                      | Non-Volatile Memory                    |  |

| OS                                       | Operating System                       |  |

| PC Program Counter                       |                                        |  |

| PCM Phase Change Memory                  |                                        |  |

| <b>PRS</b> Proportional Resource Scaling |                                        |  |

| ReRAM                                    | Resistive Random-Access Memory         |  |

| $\mathbf{RF}$                            | Random Forest                          |  |

| ROB                                      | Re-Order Buffer                        |  |

| $\mathbf{RR}$ | RiskRelief |

|---------------|------------|

| RR            | RiskRelief |

- $\mathbf{RR-N}$  RiskRelief-Nursery

- ${\bf RR-M} \qquad {\rm RiskRelief-Mature}$

- **SER** Soft Error Rate

- **SRAM** Static Random Access Memory

- **STP** System Throughput

- **STT** Spin-Transfer Torque

- **SVM** Support Vector Machines

- **TLB** Translation Lookaside Buffer

- **TSV** Through-Silicon Via

### Chapter 1

### Introduction

### 1.1 Motivation

In this section, we first focus on the challenges related to managing emerging hybrid memory systems and then motivate the need for novel simulation and prediction techniques for exploring and evaluating future large-scale systems.

#### 1.1.1 Soft Error Reliability in Hybrid Memory Systems

High-bandwidth memory (HBM) is very popular in emerging hybrid memory designs as it satisfies the ever-evolving bandwidth requirements of new throughput-oriented compute platforms. HBM delivers  $4-8\times$  higher bandwidth than traditional DRAM memory using 3D die-stacking. Unfortunately, HBM is limited in capacity and has a high soft error rate due to high bit density and new failure modes [84, 130]. Combining HBM and DRAM into a hybrid memory system can meet the need for high capacity provided by DRAM and benefit from high bandwidth provided by HBM. The reliability of hybrid memory systems, however, is still a concern with no proper management, especially for the HBM partition.

Hybrid memory systems are typically managed through hardware and operating system (OS) approaches. For example, HBM is organized as a cache for conventional DRAM memory in hardware approaches [43, 44, 89, 96, 107] and OS solutions map frequently accessed pages to HBM [135, 145, 146, 165]. The aforementioned proposals intensively focus on improving performance for hybrid memories, leaving the reliability problem as an open question. Soft error rates in production systems are continuously increasing, and they grow proportionally with information density [98]. Researchers have recently refocused their attention on addressing the low reliability of emerging memory systems but faced new challenges with proposals based on existing techniques. Specifically, it is insufficient to tackle the reliability problem using hardware-only approaches because they will require impractical error detection and correction capabilities [117]. The OS-based approach leverages performance and reliability for a heterogeneous memory architecture but it operates at a coarse-grained page granularity and frequent page migrations incur significant performance penalties [69].

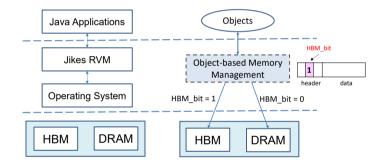

Fortunately, garbage collection in managed programming languages provides a novel insight to manage data in hybrid memory systems. In this thesis, we focus on how to improve the reliability of hybrid HBM-DRAM systems while delivering high performance and memory capacity. The subchallenges include: (1) how to quantify the performance and reliability characteristics of applications executing on the target system, (2) how to predict the hotness and risk of allocated data to guide data management, and (3) how to design a data management policy and organize hybrid memory partitions.

#### 1.1.2 Large-Scale System Simulation

Computer architects extensively rely on simulation to steer future processor research and development. Simulating architecture and predicting performance for a future computer system is a critical and challenging problem. Considerable approaches have been proposed to tackle this challenge from the perspective of either system simulation or performance modeling.

The traditional approach is to deploy detailed architectural simulations such as cycle-accurate and cycle-level simulation. However, simulating every detail of the target system increases the simulation complexity and incurs extremely high simulation time overheads. Scaling down workloads speeds up the simulation by selecting representative regions of an application to execute on the system and extrapolating the evaluated results to the whole execution process. This method saves simulation time to some extent but leaves a challenging problem for system simulation – that is, simulation infrastructures may not support simulating a large-scale computer system because of infrastructure limitations or insufficient compute and memory capacities in the simulation host system.

Performance modeling is an alternative approach to model interactions in a designed processor. ML-based techniques first train prediction models using simulation results obtained from detailed simulations and then evaluate performance or other metrics for the target system through prediction models. The key challenges of ML-based models are: (1) it is time-consuming to obtain sufficient and representative training samples from detailed simulations, and (2) such models provide limited insight into the evaluated system by treating the system as a black box. Analytical models, on the other hand, use mathematical formulas to model application behavior executing on a designed system based on simplifying assumptions and first principles. Application profiling is a one-time cost and the performance estimation is quite fast because it only contains a set of mathematical equations, making it suitable for a fast, earlystage architecture exploration. However, the lack of modeling overlap effects and tracking timing-sensitive behavior makes analytical models infeasible to simulate increasingly large systems.

In this thesis, we target efficient and accurate architectural simulation for future large-scale systems. Specifically, we combine architectural simulation with machine learning techniques to predict performance for large-scale systems based on detailed simulation of a scaled-down configuration of the target system. The key challenges involve how to construct representative scale models for the target system and how to build an accurate extrapolation model based on the scale model predictions.

#### 1.1.3 Managed Language Simulation

Multiprogrammed managed language workloads have received considerable attention from computer architects due to the emerging fields of cloud computing and micro-services [12, 67, 80, 120, 168]. Fast and accurate architectural simulation of multiprogrammed managed language workloads is thus becoming an increasingly critical problem.

Managed programming languages, such as Java, Python or JavaScript, expose a higher level of abstraction to the programmer than native programming languages like C and C++. Higher abstraction characteristics of managed programming languages incur much more memory allocation [5, 194], which stresses the memory subsystem and further increases simulation time compared to the simulation of workloads written in native programming languages. Another reason for the high simulation time of managed language workloads is the presence of a runtime environment. For example, the Java Virtual Machine (JVM), a widely-used language runtime, provides bytecode interpretation, justin-time compilation, and garbage collection to facilitate faster development times and to provide platform independence. These services run in their own context, and increase the overall execution and simulation time [2, 33, 132]. As a result, simulating a Java workload requires simulation of the entire application, including the overhead introduced by the just-in-time compiler and the garbage collector. A single-instance Java workload that we simulate executes up to 30 billion instructions and multiprogramming undoubtedly increases the simulation overhead due to contention in shared resources. A final factor that inhibits fast simulation of multiprogrammed managed language workloads is the internal synchronization of parallel simulators. Simulators, such as Sniper [36], provide high-speed, parallel simulation for multithreaded and multiprogrammed workloads. To keep the simulation correct and accurate, synchronization of cores and shared resources is required, which inhibits the scalability of simulation time for multiprogrammed managed language workloads. All these challenges motivate our newly proposed scale-model architectural simulation methodology for simulating a large-scale system with multiprogrammed managed language workloads executing on it.

### **1.2** Key Contributions

This thesis makes four major contributions.

#### Contribution #1: Allocation-Site Homogeneity

Garbage collection (GC) offered by managed programming languages automatically manages virtual heap memory and relieves the programmer from performing manual memory management where the programmer specifies how to allocate and deallocate objects. More specifically, generational GCs place newly allocated objects in a small nursery space and copy nursery survivors to a large mature space during a nursery collection. To address the performance and reliability challenges for a hybrid HBM-DRAM memory, we need to profile the application execution on the target system. We build upon two notions, namely hotness and risk, to quantify the performance and reliability characteristics of the evaluated applications. Intuitively, hotness refers to how frequently an object is accessed and risk refers to how susceptible an object is to soft errors. The simple placement of hot objects in HBM improves performance, while significantly hurting the reliability of the overall system. The first insight is to place objects in HBM versus DRAM based on their hotness and risk to benefit from both memory components – that is, delivering high reliability while achieving high performance.

We start by quantifying the distribution of object hotness and risk for several representative benchmarks. We observe that a large fraction of matureobject accesses are captured by a relatively small fraction of the mature heap. For benchmark Fop for example, 90% of the mature-object accesses are concentrated to only 32% of the mature heap. This observation suggests an opportunity to allocate a small fraction of hot objects in HBM to improve performance while placing the bulk of the mature heap in DRAM to exploit its capacity. On the risk side, we report the distribution of relatively hot objects and observe a remarkable variation in risk, implying that hotness is not predictive for risk. In other words, object hotness and risk are weakly correlated. Therefore, we need a method to predict and classify objects for both hotness and risk combined.

The second key insight is that allocation site is an accurate predictor for both object hotness and risk. To demonstrate this, we first compute the hotness and risk for all objects and then compute the fraction of hotness and risk across objects for each allocation site. We define *homogeneity* of an allocation site with respect to hotness, risk or combined hotness/risk, as the fraction of objects that are classified in the same category. For example, for the combined hotness and risk metric, perfect (100%) homogeneity means that all objects allocated from a certain site are both hot and low-risk, or they are not, i.e., they are either cold or high-risk. We report the heap volume distribution over allocation-site homogeneity for hotness, risk and the combined hotness/risk and make two observations. First, heap volume increases with decreasing allocation site homogeneity. For example, a relatively small fraction of the total heap volume is covered at 100% homogeneity and the entire heap is covered at 50% homogeneity. Second, the combined metric outperforms the isolated hotness and risk metrics. For example, for 90% homogeneity, more than 97% of the heap is correctly classified for the combined metric and the percentage numbers are 79% and 72% for hotness and risk, respectively. This implies that allocation site is a more accurate predictor for hotness and risk combined, than for hotness and risk in isolation. Based on the two discussed observations, we conclude that the allocation site is a very accurate predictor for object hotness and risk, which enables the proposed garbage collection assisted with allocation-site prediction.

#### Contribution #2: Reliability-Aware Garbage Collection

We propose two reliability-aware garbage collectors for hybrid HBM-DRAM memory to minimize the soft error rate while maximizing the overall performance of the application. These collectors place hot and low-risk objects in HBM memory to improve reliability and performance, and place the remaining objects in DRAM memory to exploit its large capacity. Specifically, RiskRelief-Nursery (RR-N) places the nursery space in HBM and the rest, such as the mature space and the large object space, in DRAM. It requires minimal changes to Java runtime but is highly effective in delivering low soft error rates compared to an HBM-Only system and improving performance compared to a DRAM-Only system. RiskRelief-Mature (RR-M) also places newly allocated objects in the nursery space in HBM, and copies hot and low-risk nursery survivors to the HBM mature space instead of DRAM mature space during the nursery collection for a larger performance improvement.

We observe that mature object hotness and risk are predictable on a per allocation-site basis. Based on this observation, we propose a heuristic to classify allocation sites as DRAM and HBM. Allocation sites are classified as HBM if most of the objects they allocate are hot and low-risk. All other allocation sites default as DRAM. We generate this per allocation-site advice offline and feed it to RR-M. In turn, RR-M uses the advice during runtime to place nursery survivors in HBM or DRAM. Our proposed heuristics expose previously unseen Pareto-optimal trade-offs between execution time and soft error rate. A single profiling run generates a range of advice files for the GC runtime. Thus, depending upon factors such as environmental conditions, available HBM capacity and performance goals, a system operator can adjust the advice fed to RR-M to meet specific demands, such as exploiting the rich trade-offs between performance, SER and memory capacity.

Our experimental results show that RR-N reduces the overall soft error rate by  $18 \times$  on average compared to an HBM-Only system, while improving the performance over a homogeneous DRAM-Only system by 20%. The state-ofthe-art OS solution by Gupta et al. [69] achieves similar SER as RR-N, however, performance is substantially worse (even worse than the DRAM-Only system) due to the high cost of TLB shootdowns on modern x86 multicores [135]. Both RR-N and the prior OS approach use a modest 128 MB of HBM on a 32-core platform. RR-M uses an additional 18% of HBM capacity but delivers 29% higher performance compared to a DRAM-Only system. Higher HBM capacity affects the overall SER, and RR-M reduces SER by  $9 \times$  over HBM-Only.

The above two contributions are published in:

W. Liu, S. Akram, J. B. Sartor, and L. Eeckhout. Reliability-Aware Garbage Collection for Hybrid HBM-DRAM Memories. *ACM Transactions on Architecture and Code Optimization (TACO)*, 18(1):1–25, 2021

#### Contribution #3: Scale-Model Architectural Simulation

We propose scale-model simulation, a novel methodology to predict performance for future large-scale multicore systems. Scale-model simulation combines architectural simulation with machine learning techniques to predict performance for future systems based on a detailed simulation of a scaled-down configuration of the target system, called the *scale model*. Scale-model simulation first simulates a scale model of the target system. Performance for the target system is then predicted through extrapolation. Scale-model architectural simulation involves two key concerns: (1) how to construct scale models and (2) how to build an accurate extrapolation model based on the scale-model predictions. For the first objective, the challenge when constructing scale models for general-purpose multicore processors is how to deal with shared resources. One option is to simply scale the number of cores in the scale model while keeping the shared resources unchanged as in the target system – we refer to this approach as No Resource Scaling (NRS). We find for our suite of SPEC CPU2017 workloads that not scaling shared resources leads to largely inaccurate scale models with an average 60% prediction error (and up to 94%) for a single-core scale model versus a 32-core target system. The alternative option is to proportionally scale the shared resources – we refer to this approach as Proportional Resource Scaling (PRS). More specifically, when scaling the number of cores by a factor F in the scale model relative to the target system, the shared resources are also reduced proportionally by the same factor, i.e., LLC capacity, NoC bisection bandwidth and memory bandwidth are reduced by a factor F. We find that proportional resource scaling delivers substantially more accurate scale models, with an average prediction error of 14.7% and at most 32.2% for a single-core scale model relative to a 32-core target system.

After constructing scale models for the target system, we need to explore extrapolation techniques to yield much more accurate performance predictions for the target system based on the performance results obtained from scale models. We propose and evaluate two extrapolation methods that leverage Machine Learning (ML) to infer prediction models that predict target-system performance based on scale-model measurements, namely ML-based prediction and ML-based regression. The key difference between both methods is that MLbased regression does not require simulation runs of the target system during training, in contrast to ML-based prediction. This has important implications in practice. We have to resort to ML-based regression if it is impossible to simulate the target system for some reason (e.g., too long simulation time or other infrastructure-related limitations). We explore a variety of machine learning techniques, including decision trees, random forest and support vector machines (SVM) in the context of scale-model simulation, and we find that SVM is the most accurate. In addition, we evaluate a number of regression-based extrapolation methods (i.e., linear, power and logarithmic) and find that logarithmic regression is the most accurate.

Our evaluation using multiprogram SPEC CPU2017 workloads demonstrates high accuracy of the scale-model simulation. Considering a single-core scale model and a 32-core target system, we report that for homogeneous multiprogram workload mixes, SVM-based prediction yields an average prediction error of 6.4% (and 20.8% max error). SVM-based regression is slightly less accurate as it does not involve simulations of the target system when training the prediction model. SVM-based regression yields an average prediction error of 8.0% (and 26.4% at most). Scale-model simulation leads to substantial simulation speedups. Training the prediction model is a one-time cost that can be amortized across many predictions. Once the prediction model has been trained, scale-model simulation is fast. It only requires running a simulation of the application of interest on the single-core scale model, which is substantially faster than running a simulation of the target system, i.e., in our experimental setup in which we use Sniper [36] on a high-end 36-core Intel PowerEdge R440 server, we find that simulating a single-core scale model is  $28 \times$  faster than simulating the 32-core target system.

This contribution is published in:

W. Liu, W. Heirman, S. Eyerman, S. Akram, and L. Eeckhout. Scale-Model Simulation. *IEEE Computer Architecture Letters (CAL)*, 20(2):175–178, 2021

An extended version of this work is published in:

W. Liu, W. Heirman, S. Eyerman, S. Akram, and L. Eeckhout. Scale-Model Architectural Simulation. In *Proceedings of IEEE International Symposium on Performance Analysis of Systems and Software (ISPASS)*, 2022, Accepted

## Contribution #4: Scale-Model Simulation for Reliability-Aware Garbage Collection